# STUDY OF THE INFLUENCE OF TEMPERATURE ON THE TRANSITIONS OF THE Cds/si/CdTe HETEROSYSTEM

©Feruza A. Giyasova<sup>1</sup>, ©Khayot N. Bakhronov<sup>2</sup>, ©Murodjon A. Yuldoshev<sup>3</sup>\*, ©Ibrokhim B. Sapaev<sup>4</sup>, ©Rustamjon G. Ikramov<sup>5</sup>, ©Farkhod A. Giyasov<sup>1</sup>, Mira R. Bekchanova<sup>6</sup>, Maxmudjon M. Qaxxarov<sup>5</sup>, Hakimjon O. Abdullayev<sup>5</sup>

<sup>1</sup>Kimyo International University in Tashkent, Uzbekistan

<sup>2</sup>Tashkent University of Information Technologies named after Muhammad al-Khwarizmi, Uzbekistan

<sup>3</sup>Turan International University, Namangan, Uzbekistan

<sup>4</sup>Tashkent Institute of Irrigation and Agricultural Mechanization Engineers National Research University, Tashkent, Uzbekistan

<sup>5</sup>Namangan State Technical University, Uzbekistan

<sup>6</sup>University of Public Security of the Republic of Uzbekistan

\*Corresponding Author e-mail: murod.yuldoshev1993@gmail.com

Received September 4, 2025; revised October 18, 2025; accepted October 25, 2025

The study presents the results of an investigation into the temperature dependence of the current–voltage characteristics of CdS/Si/CdTe heterostructures fabricated by thermal evaporation. The study establishes that, as the temperature increases, an exponential rise in current is observed, attributed to the thermally activated nature of conductivity and the reduction of the potential barrier at the interfacial boundaries. In the low-temperature region, the structure exhibits diode-like behavior, whereas at higher applied voltages (20–40 V), an injection transport mechanism becomes dominant. The activation energy of 0.61 eV confirms that the thermal release of carriers from localized states governs charge transport. The results indicate the stability of the barrier height and conduction mechanism over the studied temperature range, highlighting the need to account for thermal effects in the design of photoelectric and optoelectronic devices based on CdS/Si/CdTe structures.

**Keywords:** Temperature; Heterosystem; Layer; Carrier; Mobility; Mechanism; Current; Voltage; Structure **PACS:** 64.70.kg, 73.40.Kp, 68.37.Hk

### INTRODUCTION

In recent years, there has been growing interest in the development and investigation of thin-film heterostructures based on group II–VI compounds, which are distinguished by their high photoelectric efficiency and thermal stability under operating conditions [1–3]. Among these materials, cadmium-containing compounds such as CdS and CdTe have attracted particular attention due to their direct bandgap nature, strong optical activity, and the technological simplicity of their deposition processes. These properties make them widely applicable in solar cells, photodetectors, and various optoelectronic devices [4–7]. The incorporation of a silicon layer into CdS/CdTe-based heterostructures enables more effective lattice parameter matching between the constituent layers, reduces defect density at the interfaces, and improves charge-carrier transport conditions, thereby enhancing the overall functional performance of the structure [8-10]. Such a heterostructure is considered a promising platform for developing photoconverters with a broad spectral sensitivity range. In this system, the CdS layer-a wide-bandgap semiconductor ( $E_g\approx 2.4~eV$ )-acts as a transparent window; silicon ( $E_g\approx 1.12~eV$ ) serves as a buffer and transport layer; while CdTe-a narrow-bandgap semiconductor ( $E_g\approx 1.5~eV$ )-provides efficient light absorption and charge-carrier generation [11,12]. The operational parameters of such structures are largely determined by temperature conditions, which influence the recombination rate, the potential barrier height of the p-n junction, and the carrier mobility.

The influence of temperature on the operating parameters of a photodiode is primarily determined by two fundamental diode characteristics-the ideality factor and the reverse saturation current density [13,14]. Direct-bandgap semiconductor materials such as CdS and CdTe have demonstrated high efficiency in the fabrication of thin-film photodiode structures [15,16].

To achieve the highest efficiency of photodiodes based on  $A^2B^6$  compounds, the solid solution should possess a continuously graded composition across a thickness of d << 1  $\mu$ m, ranging from CdS to CdTe [17]. The use of high-temperature processing during the formation of CdS/CdTe-based heterostructures incorporating a silicon layer leads to an increased concentration of uncontrolled impurities throughout the entire structure, including within the compound layers [18]. In CdS/CdTe heterostructures, a junction with pronounced rectifying behavior and high photosensitivity is typically formed [19, 20]. In addition to parameters such as layer thickness, doping level, bandgap width, charge-carrier mobility, and density of states, temperature effects exert a significant influence on the photoelectric characteristics and operational stability of photodiodes. Therefore, the investigation of the temperature dependence of current–voltage characteristics in CdS/Si/CdTe heterostructures represents a relevant and timely task aimed at optimizing their

Cite as: F.A. Giyasova, Kh.N. Bakhronov, M.A. Yuldoshev, I.B. Sapaev, R.G. Ikramov, F.A. Giyasov, M.R. Bekchanova, M.M. Qaxxarov, H.O Abdullayev, East Eur. J. Phys. 4, 461 (2025), https://doi.org/10.26565/2312-4334-2025-4-47

<sup>©</sup> F.A. Giyasova, Kh.N. Bakhronov, M.A. Yuldoshev, I.B. Sapaev, R.G. Ikramov, F.A. Giyasov, M.R. Bekchanova, M.M. Qaxxarov, H.O Abdullayev, 2025; CC BY 4.0 license

photoelectric properties and enhancing stability under various operating conditions. In the present study, the influence of temperature on the key operating parameters of CdS/Si/CdTe photodiode heterosystems was analyzed within the temperature range of 293–333 K. The results obtained provide insights into the temperature stability of these structures and contribute to the optimization of the performance characteristics of single- and multi-junction photodiodes, taking thermal effects into account.

#### EXPERIMENTAL PART

The investigated CdS/Si/CdTe heterosystem [21,22] was fabricated in a quasi-closed volume using the vacuum thermal evaporation method of CdS and CdTe powders onto an n-type monocrystalline silicon substrate. The substrate used was monocrystalline silicon of the KEF-600 grade, oriented along the (111) crystallographic direction, with a thickness of d=130  $\mu$ m, a diameter of D=42 mm, and a specific resistivity of  $\rho$ =607.47  $\Omega$ ·cm. The concentration of the majority charge carriers was  $N_n$ =7×10<sup>12</sup> cm<sup>-3</sup>, and the area of the resulting structure was 29 mm<sup>2</sup>. The thickness of the deposited films was d = 0.55  $\mu$ m and was determined using a MII-4 microinterferometer [21]. The films consist of microcrystalline blocks with a columnar grain structure, oriented along the growth direction and azimuthally disoriented. The grain sizes range from 50 to 100  $\mu$ m, extending through the entire film thickness. This combination of structural parameters and technological conditions ensures the formation of a high-quality heterojunction with good crystallinity and minimal interfacial defects, which is a prerequisite for obtaining stable current–voltage characteristics of the photodiode over a wide temperature range [17].

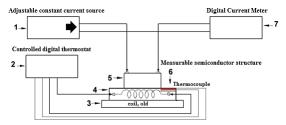

The temperature dependence of the investigated photodiode samples of the CdS/Si/CdTe heterosystem was recorded in the measuring chamber of a Carl Zeiss Jena monochromator. The temperature regime in the investigated samples was set using a heater mounted in the sample holder placed inside the measuring chamber. The set temperature from room temperature to 60 °C was measured with a copper-constantan thermocouple and maintained with a thermostat, as shown in Fig. 1.

The temperature in the studied sample 5 was controlled using a specially made low-inert heater -4, mounted in the sample holder -3, placed inside the measuring chamber. The temperature was set from room temperature to  $60^{\circ}$ C, with an accuracy of  $\pm 1^{\circ}$ C It was measured by thermocouple 6 (chromel-droplet) and maintained by digital thermostat 2, taking into account the inertia of the system. Using a high-precision adjustable voltage source -1, a fixed voltage was set, supplied to the studied sample -5. From the output of the studied sample 5, the current flowing through the semiconductor structure was supplied to a digital current meter -7, SH-300, used in the DC measurement mode.

Based on the obtained results, the dependence of current change on temperature was constructed using OriginPro 7.0.

Figure 1. Block diagram for measuring the temperature dependence of the volt-ampere characteristic

# RESULTS AND DISCUSSION

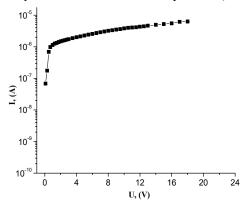

The current–voltage (I–V) characteristics of the structure were recorded in the forward direction over a wide range of current and voltage values. Assuming electrically active defects, analyzing I–V characteristics allows conclusions to be drawn about the defect structure formed within the heterosystem. Fig. 2 presents the forward branch of the I–V characteristic of the CdS/Si/CdTe heterosystem obtained at room temperature (293 K).

Figure 2. Volt-ampere characteristic of the CdS/Si/CdTe heterosystem in the forward direction at T=293 K

The current-voltage dependence is plotted on a semi-logarithmic scale. The analysis of the I-V characteristics indicates that the structure exhibits pronounced rectifying behavior. At 18 V, the rectification coefficient is ~10, confirming the diode-like behavior of the structure. Previously published research [23] presents the results of an analysis of the I-V characteristics of the CdS/Si/CdTe heterosystem.

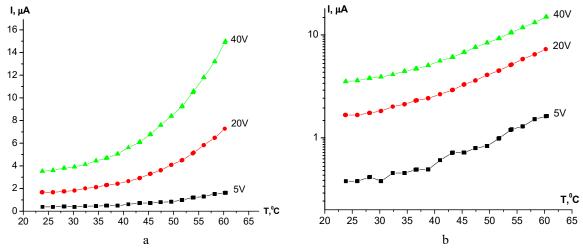

The temperature dependence of the CdS/Si/CdTe heterosystem is shown in Fig. 3 and was recorded in the forward direction over wide current change ranges at fixed voltage. The study was conducted in the temperature range T=293÷333 K.

**Figure 3.** Current–voltage characteristics of the CdS/Si/CdTe heterosystem in the forward direction (a) and their sublinear regions (b) at fixed voltage values of 5 V, 20 V, and 40 V

In the obtained dependence (Fig. 3), an exponential increase in current with rising temperature was observed, indicating a thermally activated conduction mechanism. The forward branch of the I–V characteristics at low fixed voltages (5 V) followed an exponential dependence, whereas at higher voltages (up to 40 V) a sublinear increase in current with voltage was observed. In the low-temperature region, the current remained small due to the insufficient concentration of thermally excited carriers, while at low voltages (~5 V) an exponential current growth typical of diode structures with a diffusion-controlled conduction mechanism was evident. As the temperature increased, a noticeable enhancement of conductivity occured, associated with the intensification of thermal carrier generation and a reduction in the potential barrier at the CdS/Si and Si/CdTe heterointerfaces. At a fixed voltage of 20 V, the current increase was moderate, indicating a diode-type transition dominated by thermally activated charge transport processes. However, when the fixed voltage was increased to 40 V, the current rises much more rapidly, suggesting the onset of an injection-type conduction mechanism and an additional lowering of the barrier height at the heterojunction interface upon heating. An increase in temperature above 330 K was accompanied by a growth in leakage currents, which is likely associated with the thermal ionization of deep impurity and defect levels localized at the CdS/Si and Si/CdTe interfaces. The initial portion of the temperature dependence (Fig. 3) was well approximated by a known empirical law [24].

$$I = I_0 exp (eV/ckT) (1)$$

The values of the exponent c in the exponent and the pre-exponential factor  $I_0$ , calculated from the temperature dependence (Fig. 3) for different temperatures, are given in Table 1.

Table 1. Values of the exponent c in the exponent and the pre-exponential factor Io at different temperatures

| T, K | C    | $I_0, A$              |

|------|------|-----------------------|

| 293  | 2.92 | 5.17·10 <sup>-8</sup> |

| 303  | 2.15 | 8.02·10 <sup>-8</sup> |

| 323  | 1.78 | 2.53·10 <sup>-7</sup> |

| 333  | 1.09 | 3.02·10 <sup>-7</sup> |

The transitions formed between the CdS/Si and Si/CdTe layers were high-resistance [25-27] and they mainly determined the electronic processes in the structure and the current transfer mechanism.

Dependence (1) is typical for the so-called "long" p-n diode, i.e. when  $d/L_p>1$ , where d is the base length,  $L_p=(D_p\tau_p)^{1/2}$  is the diffusion length of minority carriers,  $D_p$  is the diffusion coefficient,  $\tau_p$  is the lifetime of minority carriers. Since the electronic processes [28, 29] associated with charge modulation during current flow through the structure are largely determined by the transition high-resistance layers of CdS and CdTe, it is reasonable to take the thickness of these layers, which is approximately d≈0.55  $\mu$ m, as the base length.

Exponential dependence of current on voltage (1) for p-i-n structures, the exponent c in the exponent has the following form:

$$c = \frac{2b + ch(d/L_p) + 1}{b + 1},\tag{2}$$

where,  $b=\mu_n/\mu_p$  is the ratio of electron and hole mobilities in the CdS/Si and Si/CdTe transition layers, b=9.12 [30, 31]. Knowing b, we can find  $d/L_p=2.84$ , then we can find the diffusion length of minority carriers:  $L_p=0.71$   $\mu m$ . This allowed us to determine the product of the mobility and the minority carrier lifetime  $\mu_p\tau_p=qL^2_p/kT$ , which was obtained at room temperature (293 K) as  $1.38\times10^{-7}$  cm²/V. At T=313 K,  $\mu_p\tau_p=4.12\times10^{-7}$  cm²/V, which is e times greater than the value at room temperature; the increase in  $\mu p \tau p$  with temperature is explained by the recharging of deep centers.

The minority carrier lifetime  $(\tau_p)$  was determined by the relaxation process of nonequilibrium carriers at a low excitation level both in the mode without external voltage and at different values of the applied voltage [32, 33]. Nonequilibrium carriers were created using an electric pulse generated by a G5-63 rectangular pulse generator. The pulses had a sharp front and tail with a duration of 500-600 ns. The rise time did not exceed  $3\times10^{-9}$  s, and the duty cycle was at least  $6\times10^{-4}$  s. In the absence of external voltage, the change in the concentration of nonequilibrium carriers n over time is described by an exponential dependence:

$$\Delta n = \Delta n_0 \exp(-t/\tau),\tag{3}$$

where, t is the time and  $\tau$  is the relaxation time constant. Based on dependence (5), the value of this constant was obtained:  $\tau \approx 3.16 \times 10^{-7}$  s. Since in the structures under consideration the relaxation process was determined by the modulation of currents by minority carriers, the characteristic relaxation time corresponds to the lifetime of minority carriers, i.e.  $\tau_p \approx 3.16 \times 10^{-7}$  s.

To avoid losses caused by the voltage drop in the bulk of the CdTe film, the Fermi level should be no further than approximately 0.2 eV from the upper boundary of the valence band, and for CdS, no further than 0.08 eV from the conduction band. The situation was complicated by the fact that even ultrapure CdTe and CdS samples inevitably contain residual impurities such as Cu, Fe, Au, Ag, As, P, and others in concentrations reached 10<sup>15</sup>-10<sup>16</sup> cm<sup>-3</sup> [34-35]. In addition to uncontrolled impurities, electrically active defects arised in the material, which were formed during its synthesis, as well as during mechanical or chemical treatment. For example, Cd vacancies are capable of forming singly or doubly charged acceptor states, and in combination with impurities such as Cl, they form donor complexes (known as A-centers). Te vacancies and Te atoms in interstitial sites or at Cd sites also behaved similarly to impurities of various natures. As a result, both shallow and deep acceptor and donor levels were inevitably present in the CdTe band gap, making this material a partially compensated semiconductor [36].

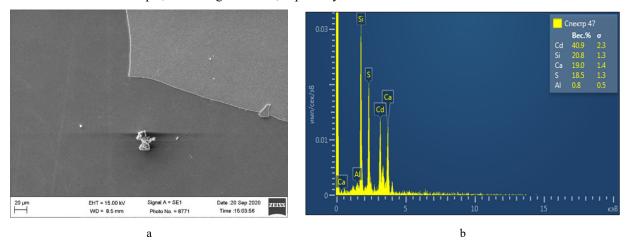

Fig. 4 shows SEM images of a thin-base CdS film grown on a silicon substrate of n-type CdS/Si/CdTe heterosystem and mass fractions of cadmium (Cd) elements and residual impurities in percentage. It can also be seen that the back side of the sample, consisting of silicon, is partially covered with a thin CdS film.

Figure 4. SEM images of the surface (a) and elemental analysis (b) of a thin base layer based on n-type CdS of the CdS/Si/CdTe heterosystem

It is known that, in the general case, the current–voltage characteristic (I–V characteristic) of a p–n junction under forward bias can be expressed by the following formula [24]:

$$I = I_s exp \frac{qV}{nkT},\tag{4}$$

determine the voltage drop across the p-n junction, which has the following expression:

$$V = \frac{nkT}{q} \ln \frac{I}{I_s},\tag{5}$$

According to the dependencies (Fig. 5) measured on experimental samples at different temperatures, it was noted that with a change in temperature, the coefficient of non-ideality also changed. In this case, the coefficient of non-ideality changes linearly inversely proportional to the temperature (1/T) and is expressed as follows:

$$n = n_0 + \frac{T_0}{T} \tag{6}$$

where,  $n_0$  and  $T_0$  are constants of the empirical formula describing the dependence of the non-ideality coefficient on temperature. For the experimental samples under study at  $T_0$ =310 K, the value of  $n_0$  is 0.72.

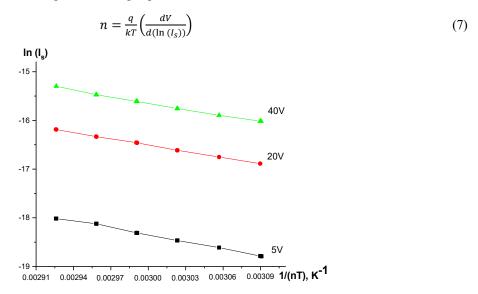

In practical calculations, the ideality factor is determined from the slope of the linear section of the I–V characteristic (Fig. 5) in semilogarithmic coordinates using the following expression:

Figure 5. Arrhenius dependence of the pre-exponential factor for the CdS/Si/CdTe heterosystem

The graph shown in Fig. 5 illustrates the dependence of the logarithm of the saturation current (lnI<sub>s</sub>) on the inverse temperature (1/(nT)) for the CdS/Si/CdTe heterosystem at various fixed voltages: 5 V, 20 V, and 40 V. The linear nature of the dependencies corresponding to voltages of 20 V and 40 V indicates a thermally activated mechanism of saturation current conduction, which follows an exponential relationship described by expression (8) [24, 37].

$$I_s = I_{s0} exp\left(-\frac{\Delta E}{nkT}\right),\tag{8}$$

where,  $\Delta E$  - activation energy, k is the Boltzmann constant, T is the absolute temperature, and n is the ideality factor of the junction.

The negative slope of the temperature dependences of the logarithm of the saturation current indicates an increase in current with rising temperature (decreasing 1/(nT)), which is characteristic of diode structures where charge transport occurs via thermoelectronic emission across the potential barrier. The parallelism of the lines corresponding to different applied voltage values indicates that the activation energy remains constant within the studied temperature range, confirming the stability of the barrier height and the preservation of the charge transport mechanism [23,38]. At higher fixed voltages, an increase in the saturation current values is observed, which is associated with a reduction in the effective potential barrier height and an enhancement of injection processes in the heterojunction region. The linear dependence:

$$ln(I_s) = f(1/nT)$$

(9)

confirms the thermally activated nature of the saturation current and allows for the evaluation of the energy parameters of the barrier junction in the CdS/Si/CdTe structure.

From the temperature dependence (Fig. 5) of the CdS/Si/CdTe heterosystem, the activation energy of charge carriers was estimated to be  $\Delta E \approx 0.61$  eV, while the saturation current at the junctions was  $I_so=6.3\times10^{-8}$  A. The obtained activation energy value indicates a thermally activated conduction mechanism, in which charge transport is governed by the thermal release of carriers from localized energy states or by their overcoming of the potential barrier at the heterojunction interface. Based on the dependence shown in Fig. 5 and according to expression (7), the ideality factor was calculated to be n=3.6, which indicates a combined current transport mechanism in the CdS/Si/CdTe heterosystem [39,15]. Along with the diffusion transport of charge carriers, recombination and injection processes make a significant contribution to conductivity, as well as the influence of localized energy states and the inhomogeneity of the potential barrier at the interfacial boundaries [15].

According to the literature [24], the specific resistance of the material at a given temperature is determined by the concentration of the majority charge carriers (n) according to the expression  $\rho=1/q\mu_n n$ . In the CdS/Si/CdTe heterosystem at room temperature (293 K), the carrier concentration is about  $10^{11}$  cm<sup>-3</sup> and increases with increasing temperature, reaching up to  $2\times10^{12}$  cm<sup>-3</sup> at 333 K. This indicates that the studied structure is a highly compensated material in which the concentration of ionized defect complexes of the  $(V^{-2}_{Cd}D^+)$  - type is about  $10^{11}$  cm<sup>-3</sup> at room temperature.

#### **CONCLUSIONS**

The conducted studies have shown that temperature has a significant effect on the I–V characteristics of the CdS/Si/CdTe heterosystem. With increasing temperature, an exponential rise in current was observed, which is attributed to the thermally activated nature of conductivity and the reduction of the potential barrier at the interfacial boundaries. In the low-temperature region, the current remained small, whereas at low voltages (~5 V) the structure exhibited diode-like behavior characteristic of a diffusion-controlled carrier transport mechanism. When the applied voltage was increased to 40 V, an injection-type conduction mechanism stayed dominant, caused by a reduction in the barrier height upon heating. The observed increase in current with temperature indicates a decrease in the effective barrier height, confirming the stability of the electronic properties of the junction within the investigated temperature range.

The study of the temperature dependence in the sublinear region revealed that the deep energy levels within the structure are continuously distributed, with their concentration increasing toward the mid-gap region. It was established that the  $\mu p \tau p$  parameter in the heterosystem increases with temperature: at T=293 K,  $\mu_p \tau_p$ =1.38×10<sup>-7</sup>cm²/V, while at T=313 K,  $\mu_p \tau_p$ =4.12×10<sup>-7</sup> cm²/V. Based on the measured specific resistivity of the heterostructure at the corresponding temperatures, the concentration of the majority charge carriers was determined to be approximately 10<sup>11</sup>cm<sup>-3</sup>, increasing to about 2×10<sup>11</sup> cm<sup>-3</sup> with rising temperature.

The temperature dependence of the pre-exponential factor  $I_0$  in the exponential region of the current–voltage characteristics indicates a complex variation in the equilibrium charge carrier concentration within the CdS/Si/CdTe heterosystem. This behavior is attributed to the influence of deep energy levels, recombination centers, and the potential distribution features at the interfacial boundaries. It has been established that the conduction process in the CdS/Si/CdTe heterosystem exhibits a thermoactivated character. The activation energy of 0.61 eV suggests that charge transport was governed by the thermal release of carriers from localized states or by their surmounting of the potential barrier at the heterojunction interface.

The obtained results confirm the stability of the barrier height and the invariance of the carrier transport mechanism within the investigated temperature range, while also demonstrating the enhancement of injection processes under higher applied voltages. The revealed regularities highlight the necessity of accounting for temperature effects in the design and operation of photoelectric and optoelectronic devices based on CdS/Si/CdTe structures. The findings can be utilized to optimize the parameters of photoconverters and optical memory devices operating over a wide temperature range.

# ORCID

© Feruza A. Giyasova, https://orcid.org/0000-0003-0746-4986; © Murodjon A. Yuldoshev, https://orcid.org/0000-0002-9722-9439

© Khayot N. Bakhronov, https://orcid.org/0009-0000-4138-3149; © Farkhod A. Giyasov, https://orcid.org/0009-0003-9882-0655

© Rustamjon G. Ikramov, https://orcid.org/0000-0003-1629-1300; © Ibrokhim B. Sapaev, https://orcid.org/0000-0003-2365-1554

### REFERENCES

- [1] C. Cao, Q. An, "Elucidating thin film growth mechanisms for high-performance II–VI photovoltaic semiconductors: simulation-driven insights and challenges," CrystEngComm, 27(21), 3404-3415 (2025). https://doi.org/10.1039/D5CE00244C

- [2] S.M. Sivasankar, C. de Oliveira Amorim, and A.F. da Cunha, "Progress in Thin-Film Photovoltaics: A Review of Key Strategies to Enhance the Efficiency of CIGS, CdTe, and CZTSSe Solar Cells," J. Compos. Sci. 9(3), 143 (2025). https://doi.org/10.3390/jcs9030143

- [3] K.G. Zayas-Bazán, P.G. Zayas-Bazán, F. de Moure-Flores, and D. Jiménez-Olarte, "Development of a CdCl2 thermal treatment process for improving CdS/CdTe ultrathin solar cells," Journal of Materials Science: Materials in Electronics, (2019). https://doi.org/10.1007/s10854-019-01694-2

- [4] M. Mathew, "i- ZnO and CdS Buffer Layers for Improving the Efficiency of Copper Tin Sulphide Quantum Dot Sensitized Solar Cells," East Eur. J. Phys. (2), 258 (2025). https://doi.org/10.26565/2312-4334-2025-2-31

- [5] V.T. Mirzayev, B.J. Akhmadaliev, I.I. Yulchiev, and M.M. Madraximov, "Temperature and Infrared Quenching of Equilibrium Conductivity in CdSexS<sub>1-x</sub> Film," East Eur. J. Phys. (2), 247 (2025), https://doi.org/10.26565/2312-4334-2025-2-29

- [6] T.M. Razykov, K.M. Kuchkarov, A.A. Nasirov, M.P. Pirimmatov, R.R. Khurramov, R.T. Yuldashev, D.Z. Isakov, et al. "Mechanism of Current Performance in Thin-Film Heterojunctions n-CdS/p-Sb<sub>2</sub>Se<sub>3</sub> Obtained by the CMBD Method," East Eur. J. Phys. (4), 279 (2024). https://doi.org/10.26565/2312-4334-2024-4-29

- [7] Sh.B. Utamuradova, Z.T. Azamatov, A.I. Popov, M.R. Bekchanova, M.A. Yuldoshev, and A.B. Bakhromov, East Eur. J. Phys. (3), 278 (2024), https://doi.org/10.26565/2312-4334-2024-3-27

- [8] M. Isah, C. Doroody, K.S. Rahman, M.N. Rahman, A.A. Goje, M.E. Soudagar, T.S. Kiong, et al. "Exploring the impact of defect energy levels in CdTe/Si dual-junction solar cells using wxAMPS," Sci Rep. 27(14), 4804 (2024). https://doi.org/10.1038/s41598-024-55616-2

- [9] Sh.B. Utamuradova, Kh.S. Daliev, Sh.Kh. Daliev, S.A. Muzafarova, K.M. Fayzullaev, and G.A. Muzafarova, "Volt-Ampere Characteristics of Hetero Film Photosensitive Structure Au-CdS-nSi-CdTe-Au," East Eur. J. Phys. (4), 256 (2024). https://doi.org/10.26565/2312-4334-2024-4-26

- [10] M.S. Kukurudziak, V.M. Lipka, and V.V. Ryukhtin, "Silicon p-i-n Mesa-Photodiode Technology, East Eur. J. Phys. (3), 385 (2024). https://doi.org/10.26565/2312-4334-2024-3-47

- [11] G. Sürücü, H.H. Güllü, and Ö. Bayraklı, "Enhancement in Photovoltaic Characteristics of CdS/CdTe Heterojunction. Journal of Polytechnic, **20**(4), 801-805 (2017). https://doi.org/10.2339/politeknik.368993

- [12] M. Akramov, B. Eshchanov, S. Usanov, Sh. Norbekov, and D. Matrasulov, "Second-harmonic generation in branched optical waveguides: Metric graphs based approach," Physics Letters A, 524, 129827 (2024). https://doi.org/10.1016/j.physleta.2024.129827

- [13] M. Piliougine, L.E. Garcia-Marrero, K. Lappalainen, and G. Spagnuolo, "Influence of the temperature on the intrinsic parameters of thin-film photovoltaic modules," Renewable Energy, 240, 122068 (2025). https://doi.org/10.1016/j.renene.2024.122068

- [14] P. Dalapati, N.B. Manik, and A.N. Basu, "Influence of temperature on tunneling-enhanced recombination in Si based p-i-n photodiodes," Journal of Semiconductors, 35(8), 082001 (2013). https://doi.org/10.1088/1674-4926/35/8/082001

- [15] S.A. Mirsagatov. R.R. Kabulov, and M.A. Makhmudov, "Injection photodiode based on an n-CdS/p-CdTe heterostructure," Semiconductors, 47, 825–830 (2013). https://doi.org/10.1134/S106378261306016X

- [16] V. Qaradaghi, I. Mejia, and M. Quevedo-Lopez, "Fabrication and Analysis of Thin Film CdTe/CdS-Based Avalanche Photodiodes," IEEE Electron Device Letters, 38(4), 489 – 492 (2017). https://doi.org/10.1109/led.2017.2670523

- [17] S.N. Usmonov, S.A. Mirsagatov, and A.Y. Leyderman, "Study of the current-voltage characteristic of the n-CdS/p-CdTe heterostructure depending on temperature," Semiconductors, 44, 313-317 (2010). https://doi.org/10.1134/S1063782610030073

- [18] Y. Zheng, X. Zhang, X. Yang, Y. Tai, J. Zhang, and B. Li, "Design and Fabrication of CdTe//Si Four-Terminal Mechanical Stacked Solar Cell," IEEE Journal of Photovoltaics, 14(2), 260-264 (2024). https://doi.org/10.1109/jphotov.2023.3338862

- [19] A.E. Rakhshani, "Heterojunction properties of electrodeposited CdTe/CdS solar cells," J. Appl. Phys. 90(8), 4265-4271 (2001). https://doi.org/10.1063/1.1397279

- [20] L. Ma, W. Liu, H. Cai, F. Zhang, and X. Wu, "Catalyst- and template-free low-temperature in situ growth of n-type CdS nanowire on p-type CdTe film and p-n heterojunction properties," Sci Rep. 13(6), 38858 (2016). https://doi.org/10.1038/srep38858

- [21] F.A. Giyasova, "Development of Multilayer Photosensitive Structures Based on GaAs and Si for Optoelectronic Devices," D.Sci. thesis, Institute of Semiconductor Physics and Microelectronics, Uzbekistan (2024).

- [22] F.A. Giyasova, and M.A. Yuldoshev, "Investigation of temporal characteristics of photosensitive heterostructures based on gallium arsenide and silicon," Chalcogenide Letters, 22(2), 123–129 (2025). https://doi.org/10.15251/CL.2025.222.123

- [23] Sh.B. Utamuradova, F.A. Giyasova, K.N. Bakhronov, M.A. Yuldoshev, M.R. Bekchanova, and B. Ismatov, "Current Transfer Mechanism in A Thin-Based Heterosystem Based on A<sup>2</sup>B<sup>6</sup> Compounds," East Eur. J. Phys. (3), 325 (2025). https://doi.org/10.26565/2312-4334-2025-3-31

- [24] S.M. Sze, Y. Li, and K.K. Ng, Physics of Semiconductor Devices, 4th Edition, (Wiley, 2021).

- [25] S.R. Bera, and S. Saha, "Fabrication of CdTe/Si heterojunction solar cell," Applied Nanoscience, 6(7), 1037-1042 (2016). https://doi.org/10.1007/s13204-015-0516-5

- [26] F.Kh. Khasanov, I.B. Sapaev, B.S. Mirzaev, Q.A. Shakarov, U.T. Davlatov, and N.N. Abdusattorov, "Si-CdTe-CdS Structures of Electronic Processes," AIP Conf. Proc. 2432, 050017-1–050017-5 (2022). https://doi.org/10.1063/5.0089974

- [27] J.Sh. Abdullayev, I.B. Sapaev, N.Sh. Esanmuradova, S.R. Kadirov, and Sh.M. Kuliyev, "Mathematical Analysis of the Features of Radial p-n Junction: Influence of Temperature and Concentration," East Eur. J. Phys. (2), 220 (2025). https://doi.org/10.26565/2312-4334-2025-2-24

- [28] Sh.N. Usmonov, Sh.A. Mirsagatov, and A.Yu. Leyderman, "Study of the current-voltage characteristic of the nCdS/pCdTe heterostructure depending on temperature," Semiconductors, 44(3), 313-317 (2010). https://doi.org/10.1134/S1063782610030073

- [29] M.A. Yuldoshev, Z.T. Azamatov, A.B. Bakhromov, and M.R. Bekchanova, East Eur. J. Phys. (4), 250 (2024), https://doi.org/10.26565/2312-4334-2024-4-25

- [30] T. Jüstel, General Chemistry (Part Inorganic Chemistry) Lecture, April 2024. http://dx.doi.org/10.13140/RG.2.2.36270.93763

- [31] N.F. Zikrillayev, M.K. Khakkulov, M.H. Aripova, B.B. Ibragimova, and N.E. Iskandarov, "Electrophysical Properties of Cadmium and Sulfur-doped Silicon with Electronic Conductivity," International Journal of Advanced Research in Science, Engineering and Technology, 6(12), 12073-12076 (2019).

- [32] I.H. Smaili, and G.B. Hmida, "A Review of Minority Carrier Recombination Lifetime Measurements," International Journal for Research in Applied Science & Engineering Technology (IJRASET), 11(V), 1351-1361 (2023). https://doi.org/10.22214/ijraset.2023.51725

- [33] M. Koussour, S. Bekovb, J. Rayimbaev, A. Syzdykova, S. Muminovd, and I. Ibragimov, "Observational constraints on a generalized equation of state model," Physics of the Dark Universe, 47, 101799 (2025). https://doi.org/10.1016/j.dark.2024.101799

- [34] M. Zha, E. Gombia, F. Bissoli, A. Zappettini, and L. Zanotti, "Growth and Deep Level Characterisation of Undoped High Resistivity CdTe Crystals," Phys. Status Solidi B, 229, 15 (2002). https://doi.org/10.1002/1521-3951(200201)229:1<15::AID-PSSB15>3.0.CO;2-6

- [35] Kh.Yu. Rakhimov, H.T. Yusupov, Sh.R. Nurmatov, A. Chaves, and G.R. Berdiyorov, "Wave-packet rectification in graphene with alternating circular electrostatic potential barriers," J. Appl. Phys. 137, 144302 (2025). https://doi.org/10.1063/5.0250401

- [36] I.M. Dharmadasa, and A.A. Ojo, "Unravelling complex nature of CdS/CdTe based thin film solar cells," Journal of Materials Science: Materials in Electronics, 28(8), 16598-16617 (2017). https://doi.org/10.1007/s10854-017-7615-x

- [37] Y.B. Acharya, "Effect of temperature dependence of band gap and device constant on *I-V* characteristics of junction diode," Solid-State Electronics, **45**(7), 1115-1119 (2001). https://doi.org/10.1016/S0038-1101(01)00139-3

- [38] Sh.B. Utamuradova, F.A. Giyasova, M.S. Paizullakhanov, S.Yu. Gerasimenko, M.A. Yuldoshev, S.R. Boydedayev, and M.R. Bekchanova, "Investigation of the functional capability of modified silicon-based photodiodes structure," Chalcogenide Letters, 22(8), 753–764 (2025). https://doi.org/10.15251/CL.2025.228.753

- [39] Z. Wang, Z. Cheng, A.E. Delahoy, and K.K. Chin, "A Study of Light-Sensitive Ideality Factor and Voltage-Dependent Carrier Collection of CdTe Solar Cells in Forward Bias," IEEE Journal of Photovoltaics, 3(2), 843-851 (2013). https://doi.org/10.1109/jphotov.2013.2247095

# ДОСЛІДЖЕННЯ ВПЛИВУ ТЕМПЕРАТУРИ НА ПЕРЕХОДИ ГЕТЕРОСИСТЕМИ CdS/Si/CdTe Ф.А. Гіясова $^1$ , Х.Н. Бахронов $^2$ , М.А. Юлдошев $^3$ , І.Б. Сапаєв $^4$ , Р.Г. Ікрамов $^5$ , Ф.А. Гіясов $^1$ , М.Р. Бекчанова $^6$ , М.М. Кахаров $^5$ , Х.О. Абдуллаєв $^5$

<sup>1</sup>Міжнародний університет Кімьо в Ташкенті, Узбекистан <sup>2</sup>Ташкентський університет інформаційних технологій імені Мухаммада аль-Хорезмі, Узбекистан <sup>3</sup>Міжнародний університет Туран, Наманган, Узбекистан <sup>4</sup>Ташкентський інститут інженерів іригації та механізації сільського господарства Національний дослідницький університет, Узбекистан

<sup>5</sup>Наманганський державний технічний університет, Узбекистан <sup>6</sup>Університет громадської безпеки Республіки Узбекистан

У дослідженні представлені результати дослідження температурної залежності вольт-амперних характеристик гетероструктур CdS/Si/CdTe, виготовлених методом термічного випаровування. Встановлено, що зі збільшенням температури спостерігається експоненціальне збільшення струму, що пояснюється термоактивованою природою провідності та зменшенням потенційного бар'єру на міжфазних межах. В області низьких температур структура демонструє діодоподібну поведінку, тоді як при вищих прикладених напругах (20–40 В) домінує інжекційний механізм транспорту. Енергія активації 0,61 еВ підтверджує, що теплове вивільнення носіїв заряду з локалізованих станів керує транспортом заряду. Отримані результати свідчать про стабільність висоти бар'єру та механізму провідності в досліджуваному діапазоні температур, а також про необхідність врахування теплових ефектів при проектуванні фотоелектричних та оптоелектронних пристроїв на основі структур CdS/Si/CdTe.

Ключові слова: температура; гетеросистема; шар; носій; рухливість; механізм; струм; напруга; структура