DOI: 10.26565/2312-4334-2025-3-36 ISSN 2312-4334

# IMPACT OF LOCAL OXIDE TRAPPED CHARGE ON ELECTRICAL AND CAPACITANCE CHARACTERISTICS OF SOI FINFET

<sup>a</sup> Urgench State University, named after Abu Rayhan Biruni, Kh.Olimjan str.,14, Urgench, 220100, Uzbekistan

<sup>b</sup> Andijan State University, Universitet str.,129, Andijan, 170100, Uzbekistan

<sup>c</sup> Tashkent Institute of Irrigation and Agricultural Mechanization Engineers, National Research University,

K. Niyoziy str.39, Tashkent, 100000, Uzbekistan

\*Corresponding Author e-mail: x-mahkam@urdu.uz, x-mahkam@mail.ru

Received May 7, 2025; revised June 28, 2025; accepted July 19, 2025

In this work, the influence of the local oxide trapped charge on the transfer  $I_d - V_g$  characteristics and capacitance of the gate-to-source (drain) connection of the silicon-on-insulator (SOI) structure-based FinFET is simulated.  $I_d - V_g$  characteristics are simulated by using the drift-diffusion transport model. Capacitance-Voltage characteristics of the gate-to-source capacitance are simulated by using a small AC signal method. The  $I_d - V_g$  characteristics and gate-to-source (gate-drain) capacitance are investigated at different linear sizes and positions of the local oxide trapped charge along the channel. The results of the simulation show that the threshold voltage monotonically decreases with an increase in the linear size of the local charge, and gate-to-source capacitance monotonically increases with an increase in the distance between the source-channel border and the center of the local charge.

**Keywords:** FinFET; Lokal charge; Gate-to-source capacitance; p-n junction; C-V dependence

**PACS:** 85.30.Tv, 73.40.Qv, 85.30.De

# 1. INTRODUCTION

One of the main devices of nanoelectronics is field effect transistors, particularly Fin Field Effect Transistors (FinFET), which is continuously scaled over the last several decades. As a result of scaling, the characteristics of the transistors are being degraded due to short channel effects [1], [2], self-heating effect [3], [4], impact of oxide (interface) trapped charge [5], [6]. Among these degradation effects can be noted as appreciable the effects of hot carrier injection [7], [8], bias temperature instability [9]–[11], off-stress [12], and the impact of the radiation-induced charge [13]. These degradation effects are mainly connected with injection or/and generation charges in the oxide layer or at the oxide-semiconductor interface. In nanoscale FETs the random telegraph noise, induced by a single oxide (or interface) trapped charge, can also be considerable [14], [15]. The impact of these effects should be taken into account at designing and using analog as well as digital integrated circuits based on FETs.

The oxide trapped charge can affect MOSFET parameters such as threshold voltage and subthreshold slope of the transfer characteristics. Consequently, it leads to degradation of the transistor characteristics. Therefore, to determine the mechanisms and reasons of the charge trapping it is expediently develop the methods of estimation the position and distribution of the trapped charge along the channel.

Well-known methods for detecting the oxide and interface trapped charge in planar MOSFETs are methods connected with measuring current-voltage and capacitance-voltage dependencies [16]–[18]. Particularly, for this purpose, measurements of subthreshold drain current [16] and gate-to-substrate capacitance-voltage dependence [17], [18] are used. However, these methods should be modified in the case of SOI FinFET, because of specific features of the transistor's structure connected with the presence of the back oxide layer between channel and substrate. Therefore, it is important to consider and study the features of the impact of trapped charges on I-V and C-V dependences in SOI FinFET.

One of the simple and fast methods of diagnostics to detect the charge trapped in the oxide layer or at the interface is based on measurements of the capacitance-voltage characteristics of lateral source (drain)-channel p-n-junctions [19]. Experimental evidence of this method is presented in [13], [20], [21]. It is shown that the non-uniform distribution of the charge in the oxide layer or at the semiconductor-oxide interface is appropriately reflected in source-channel (drain-channel) p-n-junction capacitance [13], [19], [20], [22]. Thus, the distribution along the channel of the trapped charge should also be reflected in other capacitances connected with lateral source-channel (drain-channel) junctions.

In this work, dependencies of the drain current and threshold voltage on linear size and position of the oxide trapped charge, along the channel, are considered for SOI FinFET. The capacitance method mentioned above and first suggested for planar MOSFET [19] is modified for application in SOI FinFET. The modified method will be used to simulate the dependence of the gate-to-source capacitance,  $C_{gs}$ , on the position of the local oxide trapped charge.

Cite as: A. Atamuratov, I. Karimov, M Foziljonov, A. Abdikarimov, O. Atamuratov, M. Khalilloev, East Eur. J. Phys. 3, 357 (2025), https://doi.org/10.26565/2312-4334-2025-3-36

This paper is organized as follows. In Section 2, we present the description of the considered transistor parameters, simulation conditions, and approaches used. Simulation results with discussions are presented in Section 3. Finally, some concluding remarks are formulated in Section 4.

#### 2. TRANSISTOR PARAMETERS, SIMULATION CONDITIONS, AND APPROACHES

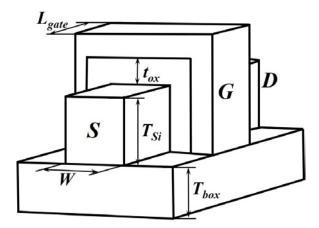

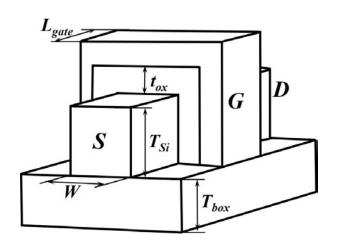

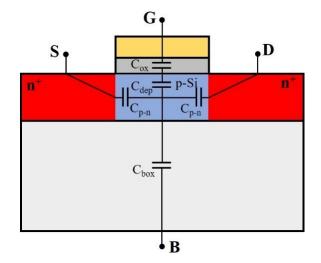

The structure of the simulated SOI FinFET is shown in Figure 1. The geometry and parameters of the simulated FinFET are shown in Table 1.

Figure 1. 3D structure of the simulated SOI FinFET

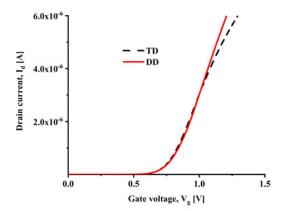

3D simulation were conducted using Advanced TCAD Sentaurus software. Transfer characteristics of the FinFET were simulated by using drift-diffusion as well as thermodynamic transport models to choose an adequate transport model. The results of the simulation are shown in Figure 2. It is shown in the figure that at gate voltages up to  $V_g - 1V$ , both  $I_d - V_g$  curves are the same. And at higher gate voltages drain current is lower at using the thermodynamic transport model, which is connected with increasing the temperature in the channel. In simulation, the range of the gate voltages was limited to 1V; therefore, the use of the drift-diffusion and thermodynamic transport models is equivalent. We used a simple drift-diffusion transport model to save resources (power and time).

| Parameter                                      | Designation | Value                                      |

|------------------------------------------------|-------------|--------------------------------------------|

| Channel doping level (p-Si)                    | $N_a$       | $1 \cdot 10^{15} cm^{-3} \text{ (n-type)}$ |

| Source and drain doping level (n-Si)           | $N_d$       | $1 \cdot 10^{20} cm^{-3}$ (n-type)         |

| Gate oxide $(HfO_2)$ thickness                 | tox         | 2.5 nm                                     |

| Channel thickness                              | $T_{Si}$    | 30 nm                                      |

| Channel width                                  | W           | 12 nm                                      |

| Back oxide layer (SiO <sub>2</sub> ) thickness | $T_{box}$   | 100 nm                                     |

| Gate length                                    | $L_{gate}$  | 25 nm                                      |

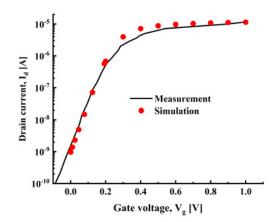

Density gradient quantum corrections were used to account for quantum effects because transistor sizes are on the nanometer scale. In the mobility model, the doping dependence and velocity saturation at high fields were taken into account. The model used in the simulation was calibrated by comparing  $I_d - V_g$  characteristics with experimental results presented in [23] (Figure 3). The experimental  $I_d - V_g$  curve presented in [23] was normalised to the width of the channel; therefore, to compare with the simulation results, it was recalculated for the whole transistor width.

In this work, the dependencies of the drain current Id and threshold voltage Vth on the position, L, and width, D, along the channel of the local oxide trapped charge were considered. The dependence of the capacitance  $C_{gs}$  of the gate-to-source (drain) connection on the position L was also considered. At considering the dependence on the position L, the width of the local oxide trapped charge D is fixed and equal to 5 nm. At considering the dependence on the width, the local oxide trapped charge is located at the drain end of the gate oxide layer and expands to the center of the oxide layer (Figure 4). The homogeneously charged area models local oxide trapped charge in the oxide layer. Charge density in the charged area is  $1 \cdot 10^{12} cm^{-2}$  (or  $4 \cdot 10^{18} cm^{-3}$ ), and it corresponds to the value that can take place in MOSFETs [18].

The choice for consideration of the gate-to-source capacitance  $C_{gs}$  is based on the following. The main idea of the capacitance method suggested in [20] to detect the oxide (interface) trapped charge is connected with the impact of

**Figure 2.** Transfer  $I_d - V_g$  characteristics simulated using thermodynamic (TD) and drift-diffusion (DD) transport models.

**Figure 3.** Calibration of the simulation model by comparing simulated and experimental [23]  $I_d - V_g$  characteristics of the SOI FinFET transistors with  $L_{gate} = 25$  nm and  $V_d = 50$  mV.

the oxide or/and interface trapped charge on lateral source-channel (drain-channel) p-n-junction capacitance,  $C_{p-n}$ , in planar MOSFET. In the case of SOI FinFET,  $C_{p-n}$  capacitance can not be measured directly because of the presence BOX layer between the source and substrate. However, this capacitance is included in the capacitance of the gate-to-source (gate-to-drain) connection (Figure 5). Therefore, changes in  $C_{p-n}$  capacitance due to oxide trapped charge should be reflected in  $C_{gs}$  capacitance.

**Figure 4.** Cross-section of the FinFET showing local oxide trapped charge.

**Figure 5.** Cross-section of the simulated SOI FinFET with pictured capacitances between contacts.

The gate-to-source connection as well as the gate-to-drain connection contains the following capacitances connected in series: gate oxide capacitance Cox, oxide-semiconductor interface depletion layer capacitance,  $C_{dep}$ , source-to-channel p-n-junction capacitance,  $C_{p-n}$ . Only in depletion mode, the depletion layer capacitance,  $C_{dep}$ , significantly contributes to  $C_{gs}$  capacitance. However, in the considered case, a transistor is in accumulation mode, because in the simulation, the p-type source (drain) region is biased by the positive pole of the voltage source relative to the gate. Thus, establishing the accumulation mode at the semiconductor surface, near the oxide-semiconductor interface, results in dismissing the capacitance  $C_{dep}$ . Consequently, the resulting capacitance  $C_{gs}$  can be expressed by the following formula (1):

$$C_{gs} = \frac{C_{p-n} \cdot C_{ox}}{C_{p-n} + C_{ox}} \tag{1}$$

here,  $C_{ox}$  is gate oxide capacitance per unit area, which does not depend on the applied voltage. Estimations show, that  $C_{p-n}$  is significantly less than Cox because width of the depletion layer of the source-to-channel (drain-to-channel) p-n-junction is approximately 0.1 µm while gate oxide thickness  $t_{ox} = 2.5$  nm. Thus, in accordance with the formula

(1)  $C_{gs}$  is determined mainly by  $C_{p-n}$ , which is very sensitive to the distribution of oxide trapped charge [13], [20]. Consequently, in this work, it is simulated the dependence of the  $C_{gs}$  on the position of the local oxide trapped charge along the channel.

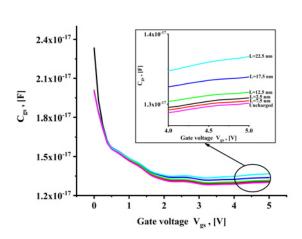

C-V dependence of the gate-to-source (gate-to-drain) capacitance were simulated with using the small AC signal method. Signal with frequency 1 MHz is used in simulation. The capacitance  $C_{gs}$  is simulated at different position of the local oxide trapped charge along the channel.

The local charge with fixed width D=5 nm, in the oxide layer at a distance L from the source-channel border (Figure 4) impacts on the carrier distribution in the channel. Consequently, this impact should be reflected in the source-to-channel junction capacitance and hence in the C-V dependence of the gate-to-source capacitance.

FinFET has symmetry relative the channel center, hence the gate-to-source and gate-to-drain capacitances should be same. Therefore, in the following, mainly the gate-to-source capacitance is considered.

#### 3. SIMULATION RESULTS AND DISCUSSIONS

#### 3.1. Impact of the local charge on electrical characteristics

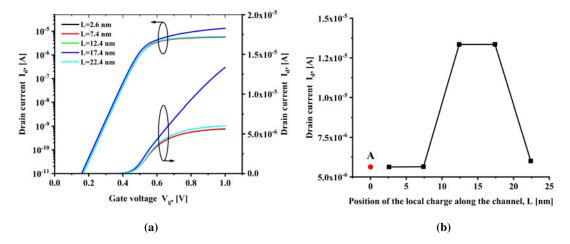

Figures 6 and 7 illustrate the simulation results regarding the dependence of drain current on the gate voltages at different positions and the width of the local oxide trapped charge. The figures demonstrate that the local oxide trapped charge considerable influence on the transfer  $I_d - V_g$  curve, especially in the region above the threshold voltage.

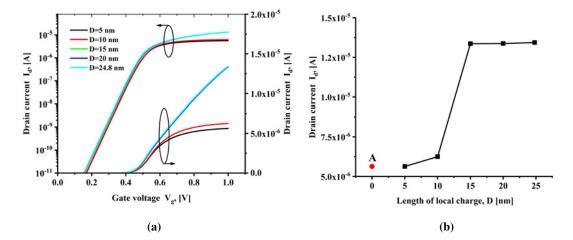

Figure 6b presents the simulation results depicting the dependence of the drain current above threshold voltage on the position L of the local oxide trapped charge. The figure demonstrates that the dependence is nonmonotonic. The drain current is maximal at the position of the local charge near the channel center. However, the dependence of the drain current on the width D is monotonic with saturation at higher D (Figure 7b). The observed behaviors of the drain current can be attributed to the appropriate behavior of the threshold voltage (Figure 8).

**Figure 6.** (a)  $I_d - V_g$  characteristics at various position, L, of the local oxide trapped charge. (b) Dependence of the drain current, at  $V_g$ =1V,  $V_d$ =0.75V, on the position, L, of the local oxide trapped charge. Point A corresponds to the case of without oxide trapped charge.

The behavior of the drain current at the change of the position and linear size of the local oxide trapped charge is correlated with the behavior of the threshold voltage. A decrease in the threshold voltage leads to an increase in the drain current and vice versa; an increase in the threshold voltage leads to a decrease in the drain current. The observed changes of threshold voltage with change of the position and width of the local oxide trapped charge can be understood in terms of the change of the distribution of channel surface potential and the corresponding inversion layer carrier concentration along the channel, induced by the field of the local trapped charge.

Originally, in case of absence, the local oxide trapped charge, potential distribution along the channel surface has a bell-shape with a maximum in the middle of the channel and with approximately zero value near the metallurgical border of the source-channel and drain-channel p-n junctions [25]–[27]. Hence, the maximal impact of the local oxide trapped charge on potential distribution and consequently on threshold voltage, can take place at the position of the local charge in the center of the channel. Figure 8a illustrates an appropriate relationship between threshold voltage and position of the local oxide trapped charge.

The threshold voltage shows a monotonic dependence on the linear size of the local charge, D (Figure 8b). This behavior of the threshold voltage is the same as the dependence of threshold voltage on the value of oxide trapped charge in planar long-channel MOSFET [15]. Hence, determining the shift of threshold voltage allows estimating the value of oxide

**Figure 7.** (a)  $I_d - V_g$  characteristics at various widths, D, of the local oxide trapped charge. (b) Dependence of the drain current, at  $V_g$ =1V,  $V_d$ =0.75V, on the width, D, of the local oxide trapped charge. Point A corresponds to the case of absence of the oxide trapped charge.

**Figure 8.** Threshold voltage dependencies on the position, L, (a) and the width, D, (b) of the local oxide trapped charge. Point A corresponds to the case of absence of the oxide trapped charge.

trapped charge in SOI FinFET using the method suggested in [16]. In case of a change in the slope of the subthreshold I-V curve, it also should be accounted for in estimating the change in threshold voltage.

#### 3.2. Impact of the local charge on gate-to-source (gate-to-drain) capacitance

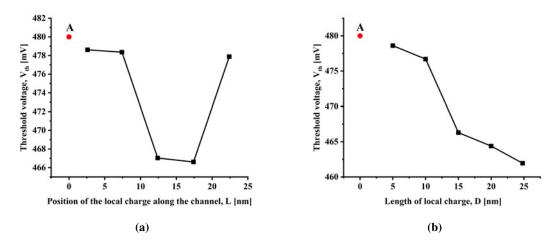

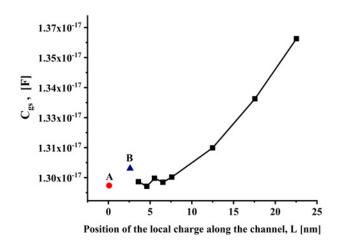

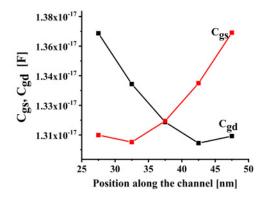

Figure 9 illustrates the simulation results regarding the C-V dependence of the gate-to-source capacitance,  $C_{gs}$ , for different position, L, of the local oxide trapped charge. The figure demonstrate that the capacitance  $C_{gs}$ , at high applied voltages is significantly and monotonically depends on L (Figure 10). The position corresponding L=2.5 nm (point B in Figure 10) is an exception in this dependence. This is attributed to the fact that in this position the local charged area is in contact with the end of the oxide layer. Consequently, the edge effect is manifested, leading to a considerably high capacitance  $C_{gs}$ ,

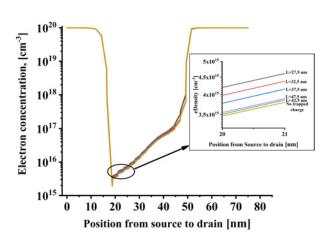

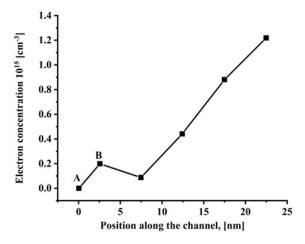

The observed increase in the capacitance  $C_{gs}$  is linked to the impact of the local trapped charge on carrier concentration within the channel. Indeed, Figure 11 demonstrates that trapping of the charge in the oxide layer leads to an increase in the carrier concentration near the channel surface at all positions of the local charge. In accordance with the definition of capacitance, this results in higher capacitance  $C_{gs}$ . In fact, by definition, the capacitance is defined in accordance with formulas (2),

$$C_{gs} = \frac{dQ_V}{dV} \tag{2}$$

**Figure 9.** C-V dependence of gate-to-source capacitance  $C_{gs}$  at different positions of the local trapped charge.

**Figure 10.**  $C_{gs}$  dependence on L at  $V_{gs}$ =4.5 V. Point A corresponds to  $C_{gs}$  when the local trapped charge is absent, point B corresponds to the position of the local trapped charge at the source end and is in contact with the oxide end (L=2.5 nm).

where  $dQ_V$  is a change of the charge in the capacitor  $C_{gs}$  at a change in the applied voltage by  $d_V$ . Trapping of the local charge into the gate oxide layer leads to adding a charge  $dQ_{LC}$  in capacitance  $C_{gs}$ , besides  $dQ_V$  Therefore, the formula (2) can be rewritten by the following expression (3)

$$C_{gs} = \frac{dQ_V + dQ_{LC}}{dV} \tag{3}$$

It follows from this expression that the capture of local charge leads to an increase in the capacitance  $C_{gs}$

**Figure 11.** Distribution of electron density along the channel at depth 2nm from the channel surface, at different positions L of the local oxide trapped charge.  $V_{gs} = 4.5 \text{ V}$

**Figure 12.** Dependence of the electron density in the channel at a depth of 2 nm from the surface on the position of the local oxide trapped charge. Point A corresponds to the case without oxide trapped charge, and point B corresponds to the position of local charge L=2.5 nm.  $V_{gs} = 4.5 \text{ V}$

The charges  $dQ_V$  and  $dQ_{LC}$  are caused by applied voltage and trapped charge, respectively, which are proportional to the change of carrier concentration in the channel. Figure 12 illustrate dependence of the electron density in the channel at a depth 2 nm from the surface on position of the local oxide trapped charge. This dependence correlate with dependence of  $C_{gs}$  on the position of local trapped charge shown in Figure 10.

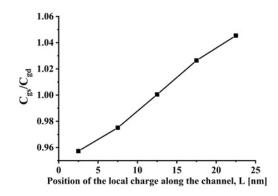

The structure of FinFET has symmetry relative vertical axis passing through the channel center, therefore dependence of gate-to-drain capacitance,  $C_{gd}$ , on position L should be the same as the dependence of  $C_{gs}$  on position L, but with reversed character. It means that  $C_{gd}$  should decrease with increasing L. Indeed, such a character of the dependence is seen in the dependence of  $C_{gd}$  on L, carried out from simulation (Figure 13). The relationship between  $C_{gs}$  and  $C_{gd}$  dependences on the L can be used to estimate the position of the local trapped charge along the channel. For this purpose, the dependence of the ratio  $C_{gs}/C_{gd}$  on L can be used (Figure 14).

**Figure 13.** Dependence of  $C_{gs}$  and  $C_{gd}$  on the position of the local oxide trapped charge, L, along the channel.

**Figure 14.** Dependence of the ratio  $C_{gs}/C_{gd}$  on the position of the local oxide trapped charge, L, along the channel.

Figure 14 demonstrates that in the case of trapping the local charge at the source side relative to the channel center, the ratio  $C_{gd}/C_{gs}$  is less than 1. Value of the ratio  $C_{gd}/C_{gs}$  is more than 1 in case of localisation the trapped charge at drain side relative the channel center. In case of localization the trapped charge in the center between source and drain end, the value of the ratio  $C_{gd}/C_{gs}$  is equal to 1.

#### 4. CONCLUSIONS

Simulation results show, that the threshold voltage monotonically depends on the linear size, D, along the channel of the charge trapped at drain end of the oxide layer. It allows to estimate integral value of trapped charge in oxide layer in the SOI FinFET as well as in planar MOSFET.

At high applied voltages, gate-to-source capacitance,  $C_{gs}$ , monotonically depends on the position of the local oxide trapped charge along channel.  $C_{gs}$  monotonically increase with increase distance between source and center of the local charge. Such dependence is explained by the influence of the local charge on the carrier distribution at the surface of the channel. The position of the local charge at the end of the oxide layer is an exception in the mentioned above dependence due to edge effect.

It is shown that the ratio  $C_{gd}/C_{gs}$  depends linearly on the position of the local oxide trapped charge along the channel in SOI FinFET. This dependence allows to develop a method to detect the charge in oxide layer and to estimate the distribution of the oxide trapped charge along the channel.

#### Acknowledgments

The authors are thankful to Prof. R. Aliev from the Andijan State University for participating in discussing the results.

### ORCID

**(b)** Atabek Atamuratov, https://orcid.org/0000-0003-2173-3783; **(b)** Ibroximjon Karimov, https://orcid.org/0009-0002-5714-8658; **(b)** Mirzabahrom Foziljonov, https://orcid.org/0009-0005-0073-1713; **(b)** Azamat Abdikarimov, https://orcid.org/0000-0003-1220-7482; **(b)** Odilbek Atamuratov, https://orcid.org/0000-0002-5010-2692; **(b)** Makhkam Khalilloev, https://orcid.org/0000-0001-5497-6410

#### REFERENCES

- [1] A.E. Atamuratov, M.M. Khalilloev, A. Abdikarimov, Z.A. Atamuratova, M. Kittler, R. Granzner, and F. Schwierz, Nanosystems: Physics, Chemistry, Mathematics, 8(1), 75 (2017). https://doi.org/10.17586/2220-8054-2017-8-1-75-78

- [2] A.E. Atamuratov, A. Abdikarimov, M. Khalilloev, Z.A. Atamuratova, R. Rahmanov, A. Garcia-Loureiro, and A. Yusupov, Nanosystems: physics, chemistry, mathematics, 8(1), 71 (2017). https://doi.org/10.17586/2220-8054-2017-8-1-71-74

- [3] A.E. Atamuratov, B.O. Jabbarova, M.M. Khalilloev, A. Yusupov, and A.G. Loureriro, in: *Proceedings of the 2021 13th Spanish Conference on Electron Devices (CDE)*, (Sevilla, Spain, 2021), pp. 62-64. https://doi.org/10.1109/CDE52135.2021.9455728

- [4] R.P. Nelapati, and K. Sivasankaran, Microelectron. J. 76, 63 (2018). https://doi.org/10.1016/j.mejo.2018.04.015

- [5] A.E. Atamuratov, M.M. Khalilloev, A. Yusupov, J. García-Loureiro, J.Ch. Chedjou, and K. Kyandoghere, Appl. Sci. 10, 5327 (2020). https://doi.org/10.1016/j.cpc.2015.01.024

- [6] B. Kaczer, J. Franco, P. Weckx, P.J. Roussel, V. Putcha, E. Bury, M. Simicic, et al., Microelectronics Reliability, 81, 186 (2018). https://doi.org/10.1016/j.microrel.2017.11.022

- [7] J. Martín-Martínez, S. Gerardin, E. Amat, R. Rodríguez, M. Nafría, X. Aymerich, *et al.*, IEEE Transactions on Electron Devices, **56**, 2155 (2009). https://doi.org/10.1109/TED.2009.2026206

- [8] A. Jaafar, N. Soin, S.F Wan Muhamad Hatta, S.I. Salim, and Z. Zakaria, Appl. Sci. 11, 6417 (2021). https://doi.org/10.3390/app11146417

- [9] B. Kaczer, T. Grasser, P.J. Roussel, J. Franco, R. Degraeve, and L.A. Ragnarsson, et al., in: 2010 IEEE International Reliability Physics Symposium, (Anaheim, CA, USA, 2010), pp. 26-32. https://doi.org/10.1109/IRPS.2010.5488856

- [10] M.K. Bepary, B.M. Talukder, and M.T. Rahman. Appl. Sci. 12, 4332 (2022). https://doi.org/10.3390/app12094332

- [11] J. Lee, Appl. Sci. 11, 356 (2021). https://doi.org/10.3390/app11010356

- [12] N. Lee, H. Kim, and B. Kang, Appl. Sci. IEEE Electron. Device. Lett. 33(2), 137 (2012). https://doi.org/10.1109/LED.2011. 2174026

- [13] A.E. Atamuratov, A. Yusupov, and K. Adinaev, Inorganic Materials, 37(8), 767 (2001). https://doi.org/10.1023/A:1017918911606

- [14] K.S. Ralls, W.J. Skocpol, L.D. Jackel, R.E. Howard, L.A. Fetter, R.W. Epworth, and D.M. Tennant, Physical Review Letters, 52, 228 (1984). https://doi.org/10.1103/PhysRevLett.52.228

- [15] M.M. Khalilloev, B.O. Jabbarova, and A.A. Nasirov, Technical Physics Letters, 45(12), 1245 (2019). https://doi.org/10.1134/ S1063785019120216

- [16] P.J. McWhorter, and P.S. Winokur, Applied Physics Letters, 48(2), 133 (1986). https://doi.org/10.1063/1.96974

- [17] E.H. Nicollian, and J.R. Brews, MOS Physics and Technology, (Wiley-Interscience, New York, 2003).

- [18] L. Boyer, B. Rousset, J. Notingher, S. Agnel, and J.L. Sanchez, in: Proceedings of the 2010 IEEE Industry Applications Society Annual Meeting, (Houston, TX, USA, 2010). pp. 1-8. https://doi.org/10.1109/IAS.2010.5614500

- [19] A.E. Atamuratov, A. Yusupov, Z.A. Atamuratova, J.C. Chedjou, and K. Kyamakya, Applied Sciences, 10(21), 7935 (2020). https://doi.org/10.3390/app10217935

- [20] A.E. Atamuratov, D.U. Matrasulov, and P.K. Khabibullaev, Doklady Physics, 52(6), 322 (2007). http://doi.org/10.1134/ S1028335807060080

- [21] U.I. Erkaboev, S.A. Ruzaliev, R.G. Rakhimov, and N.A. Sayidov, East European Journal of Physics, (3), 270 (2024). https://doi.org/10.26565/2312-4334-2024-3-26

- [22] A.E. Atamuratov, M.M. Khalilloev, A. Yusupov, J.C. Chedjou, and K. Kyandoghere, Applied Sciences (Switzerland), 10(15), 5327 (2020). https://doi.org/10.3390/app10155327

- [23] V.S. Basker, T. Standaert, and H. Kawasaki, et.al., in: Proc. Symp. VLSI Technol. (Honolulu, HI, USA, 2010), pp. 19–20.

- [24] A.S. Starkov, Microelectron. Reliab. 54, 33 (2014). https://doi.org/10.1016/j.microrel.2013.08.015

- [25] A. Asenov, R. Balasubramaniam, A.R. Brown, and J.H. Davies, IEEE Transactions on Electron Devices, 50(3), 839 (2003). https://doi.org/10.1109/TED.2003.808465

- [26] M.G. Dadamirzaev, M.O. Kosimova, S.Boydedayev, and A.S. Makhmudov, East European Journal of Physics, (2), 372 (2024). https://doi.org/10.26565/2312-4334-2024-2-46

- [27] J.S. Abdullayev, and I.B. Sapaev, East European Journal of Physics, (3), 344 (2024). https://doi.org/10.26565/ 2312-4334-2024-3-39

## ВПЛИВ ЛОКАЛЬНОГО ЗАРЯДУ, ЗАХОПЛЕНОГО В ОКСИДІ, НА ЕЛЕКТРИЧНІ ТА ЄМНІСНІ ХАРАКТЕРИСТИКИ SOI FinFET

Атабек Атамуратов<sup>а</sup>, Іброхімжон Карімов<sup>b</sup>, Мірзабахром Фозілжонов<sup>b</sup>, Азамат Абдікарімов<sup>a</sup>, Оділбек Атамуратов<sup>c</sup>, Махкам Халіллоєв<sup>a</sup>

$^a$ Державний університет Ургенчу імені Абу Райхана Біруні, вул. Х. Алімджана, 14, Ургенч, 220100, Узбекистан  $^b$ Андіжанський державний університет, вул. Університетська, 129, Андіжан, 170100, Узбекистан

<sup>c</sup> Ташкентський інститут інженерів іригації та механізації сільського господарства – Національний дослідницький університет, вул. К. Нієзія, 39, Ташкент, 100000, Узбекистан

У цій роботі моделюється вплив локального заряду, захопленого в оксиді, на передавальні характеристики Id-Vg та ємність між затвором і витоком (стоком) транзистора FinFET на основі структури кремнію на ізоляторі (SOI). Характеристики Id-Vg моделюються з використанням моделі дрейф-дифузійного переносу. Ємнісно-напругові характеристики затвор-виток моделюються за допомогою методу малого змінного сигналу (AC). Досліджено залежність характеристик Id-Vg та ємності затвор-виток (затворсток) від різних лінійних розмірів і положень локального заряду в оксиді вздовж каналу. Результати моделювання показують, що порогова напруга монотонно зменшується зі збільшенням лінійного розміру локального заряду, а ємність затвор-виток монотонно зростає зі збільшенням відстані між межою виток-канал і центром локального заряду.

**Ключові слова:** FinFET; локальний заряд; ємність затвор-виток; p-n перехід; C-V залежність