ISSN 2312-4334

### PROBLEMS OF MASKING AND ANTI-REFLECTIVE SiO<sub>2</sub> IN SILICON TECHNOLOGY<sup>†</sup>

## Mykola S. Kukurudziak<sup>a,b</sup>

<sup>a</sup>Rhythm Optoelectronics Shareholding Company, Holovna str. 244, 58032, Chernivtsi, Ukraine <sup>b</sup>Yuriy Fedkovych Chernivtsi National University, Kotsyubyns'kogo str. 2, 58012, Chernivtsi, Ukraine E-mail: mykola.kukurudzyak@gmail.com

Received April 24, 2023; revised May 7, 2023 accepted May10, 2023

The article examines the problems of thermal oxidation of silicon. Oxidation plays an important role in planar technology, which in turn is the basis of the technology of silicon integrated circuits, photodetectors and other solid-state electronics. During our production of silicon p-i-n photodiodes, a number of systematic types of defects and deterioration of product parameters caused by the degradation of masking or anti-reflective coatings during the manufacturing process were observed. A decrease in the insulation resistance of responsive elements in multi-element photodiodes was observed, which contributed to the increase of dark currents. A decrease in the responsivity of the products due to the degradation of the thickness or structure of the anti-reflective coating during technological operations, etc., was also revealed. It was established that the reason for the decrease in insulation resistance is the formation of inversion layers at the Si-SiO<sub>2</sub> interface, the presence of which can be detected when measuring CV-characteristics. It was also established that chemical treatment of substrates with SiO<sub>2</sub> in boiling acid solutions helps to reduce the thickness of the oxide. To avoid deviation of the thickness of the film from the condition of minimum reflection, it is necessary to grow a thicker layer of anti-reflective coating. It is noted that when etching the oxide during photolithography or when removing the PSG/BSG in hydrofluoric acid, it is not permissible to remove the cassette with plates from the solution for a long time, as this leads to uneven etching of the film due to the flow of the herb on the surface of the substrate. The causes of defect formation in Si and SiO2 during oxidation are given. Thus, with improper mechanical and chemical processing of the plates, cristobalite inclusions may form in the film during oxidation. Cristobalite has a higher density than quartz glass, and the boundaries between amorphous regions and denser crystalline regions represent voids, which can be filled both by impurities from the surface and by the diffusant in the diffusion process. Also, during oxidation in silicon, packing defects are often formed. Centers of defect genesis can be mechanical damage to the plate surface or growth defects.

**Keywords:** *silicon; photodiode; oxidation; silicon oxide; volt-farad characteristic; transparent film* **PACS:** 61.72.Ji, 61.72.Lk, 85.60.Dw

Oxidation plays an important role in planar technology, which in turn is the basis of the technology of silicon integrated circuits, photodetectors and other solid-state electronics [1]. At the initial stages of the development of planar technology, oxidation was used only for the manufacture of masking coatings that prevented the penetration of impurities into certain areas of the crystals during diffusion, as well as for the creation of a protective passivating layer after the device was manufactured. Recently, SiO<sub>2</sub> began to be used as active and passive elements in silicon functional blocks [2], as well as anti-reflective coatings (ARC) in photoreceiving devices [3]; this led to a new intensive study, it would seem, of the oxidation process and the properties of the oxide layer. In particular, conditions for the growth of nanometer films of silicon oxide are actively studied and modeled, which is relevant for miniaturization and increasing the speed of electronic elements [4, 5].

To date, a large number of methods have been developed, which have become standard, and allow obtaining high-quality oxide films, in particular, uniform in thickness, perfect in structure, and possessing high insulating properties. To a greater extent, these methods were developed empirically and are based on various processes: from thermal or anodic oxidation to deposition of a film from an external source [6]. Of course, to obtain oxide films with specified electrical properties, it is necessary to strictly control the behavior of impurities in the process of film formation, which is an urgent scientific and technical task.

During our production of silicon p-i-n photodiodes (PDs), a number of systematic types of defects and deterioration of product parameters caused by the degradation of masking or anti-reflective coatings during the manufacturing process were observed. A decrease in the insulation resistance of responsive elements (RE) in multi-element PDs was observed, which contributed to the increase of dark currents ( $I_d$ ). A decrease in the responsivity of products ( $S_{pulse}$ ) due to the degradation of the thickness or structure of the ARC during technological operations, etc., was also revealed. The described types of defects required a detailed study to establish the causes of their occurrence and methods of their avoidance.

When reviewing literary sources, it is seen that many works are devoted to the electrical properties of SiO<sub>2</sub>. In particular, in a number of studies, the deterioration of the reverse characteristics is associated with the presence of positive fixed or mobile charges in the oxide film [7, 8]. Thus, a quantitative model of the formation of a fixed charge in silicon dioxide during thermal oxidation was developed in [7]. It was established that the amount of charge determines the number of internodal silicon atoms near the Si-SiO<sub>2</sub> interface, and an increase in the oxidation temperature contributes to a decrease in the value of the fixed charge due to an increase in the diffusion coefficient of internodal silicon atoms in SiO<sub>2</sub>.

<sup>&</sup>lt;sup>†</sup> Cite as: M.S. Kukurudziak, East Eur. J. Phys. 2, 289 (2023), https://doi.org/10.26565/2312-4334-2023-2-33

Information about the degradation of oxide films and the influence of these factors on the responsivity of the PDs was not found in the literature. There are also no technological recommendations for avoiding the degradation of the insulation resistance of REs in multi-elements PDs. Accordingly, the study of the causes of the appearance and methods of avoiding the degradation of the masking and anti-reflective oxide films in the technology of silicon *p-i-n* PDs is the purpose of this work.

#### **EXPERIMENTAL**

The research was carried out on silicon four-element p-i-n PDs with a guard ring (GR) designed to detect radiation with a wavelength of  $\lambda$ =1064 nm. The production was carried out by diffusion-planar technology according to the technological regimes given in [10]. The starting material was single-crystal dislocation-free p-type silicon with orientation [111],  $\rho \approx 18$ -22 k $\Omega \cdot$ cm and  $\tau \approx 1.8$ -2.2 ms. The technological process consisted of a complex of thermal operations and photolithography: semiconductor substrates were oxidized; photolithography was carried out to create windows for phosphorus diffusion; diffusion of phosphorus (predeposition) to the front side to create  $n^+$ -type REs and GR; drive-in of phosphorus in an oxygen atmosphere to redistribute the alloying impurity, increase the depth of the  $n^+$ -p-transition and form a anti-reflective coating; diffusion of boron to the reverse side of the substrate to create a  $p^+$ -type ohmic contact; photolithography for creating contact windows; sputtering of Cr-Au on the front and back sides.

Masking SiO<sub>2</sub> was formed during the first thermal operation at a temperature of T=1423 K according to the principle of dry-wet-dry oxidation [5]. Considering that the thickness of silicon oxide, which completely masks from the long-term diffusion of phosphorus at T=1323 K, reaches 0.3-0.4 µm [11], the thickness of the masking SiO<sub>2</sub> reached  $d_{SiO2}\approx0.6$ -0.7 µm. This thickness is also chosen taking into account the redistribution of phosphorus in the oxide during subsequent thermal operations.

Anti-reflective silicon oxide was formed during the drive-in of phosphorus in an atmosphere of dry oxygen at a temperature of T=1423 K. The thickness of SiO<sub>2</sub> was 0.18-0.19  $\mu$ m, which corresponds to the minimum reflection condition [12]:

$$\frac{\lambda}{4} = nd_{SiO_2} \tag{4}$$

where  $\lambda$  is the working wavelength; n the refractive index of SiO<sub>2</sub>;  $d_{SiO_2}$  is the thickness of the anti-reflective film. To study the structural perfection of the surface of the substrates after thermal operations, selective etching was carried out in Sirtle's etchant [13].

After oxidation and each subsequent thermal operation, the high-frequency volt-farad (CV) characteristics of the metal-oxide-semiconductor-structures (MOS) were measured at a frequency of 30 kHz, which made it possible to predict the final parameters of the products.

The level of pulsed monochromatic sensitivity of PDs was determined at  $\lambda$ =1064 nm, bias voltage  $U_{bias}$ =120 V and pulse duration  $\tau_i$ =500 ns.

An important parameter of multi-element PDs with GR is the resistance of the isolation of the REs between themselves and the insulation resistance of the REs and the GR, the decrease of which leads to an increase in the photocoupling coefficient and dark currents. Determination of insulation resistance of REs and GR ( $R_{con}$ ) was carried out according to the method given in [14] with  $U_{bias}$ =2 V and load resistance  $R_i$ =10 k $\Omega$ .

The thickness of the oxide films was measured by the ellipsometric method.

# RESULTS OF THE RESEARCH AND THEIR DISCUSSION A) Study of CV-characteristics

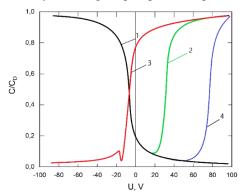

Measuring the CV characteristics of MOS structures at the initial stages of manufacturing makes it possible to estimate the final parameters of the products. Thus, in the case of p-i-n PDs manufacturing, the technological route consisted of 4 thermal operations, after each of which (except for phosphorus predeposition) CV-characteristics were measured. From the volt-farad characteristics, it is possible to determine the charge level in the oxide and detect the presence of inversion layers (IL) at the Si-SiO<sub>2</sub> interface. A typical CV-characteristic of the MOS structure for p-type silicon is shown in Fig. 1 (curve 1). When the number of charged states at the interface of two phases increases, the curve may shift to the left relative to the ordinate axis. As mentioned above, this leads to an increase in dark currents. But sometimes the formation of inversion layers at the Si-SiO<sub>2</sub> interface is observed, which form surface conductive leakage channels and reduce the insulation resistance between the REs.

The formation of ILs is possible both during the formation of a masking coating and during subsequent thermal operations. On Fig. 1 shows typical curves of volt-farad characteristics of MOS structures with inversion layers (curves 2-4). Curve 3 describes the case of doping of the silicon surface with uncontrolled impurities during oxidation, which led to a change in the conductivity type of the silicon surface to the opposite. Such a case is also possible in the presence of hydrochloric acid residues after purging quartz reactors for the purpose of cleaning from alkali metals. Curves 2 and 4 describe the case of the formation of inversion layers during the phosphorus dispersal and boron diffusion operations.

Figure 1. CV-characteristics of MOS structures: 1 – typical characteristic for p-type silicon; 2-4 – inverted characteristics

In the case of the formation of ILs during oxidation, it is necessary to etch the oxide and doing re-oxidation. The insulation resistance of REs and GR in samples with CV-characteristics of the Curve 2 type (Fig. 1) reached  $R_{con}\approx 1-10~\text{k}\Omega$  at  $R_{con}\approx 5-15~\text{M}\Omega$  for serial PDs. And dark current of GR  $J_{GR}\approx 7-36~\text{mA/cm}^2$  at  $J_{GR}\approx 3.6-36~\mu\text{A/cm}^2$  ( $U_{bias}=120~\text{V}$ ) for serial products. It is impossible to accurately measure the REs of defective PDs, since it constantly increased due to the flow of charge carriers from the GR. It is possible to fix only the initial value, which reaches  $J_d \ge 26~\mu\text{A/cm}^2$  at  $J_d = 65-130~\text{nA/cm}^2$  for serial samples. In the case of SiO<sub>2</sub> etching and re-oxidation, a decrease in dark currents is observed, but as experiments show, after re-oxidation, the values of  $I_d$  and  $I_{GR}$  are slightly higher than in serial products. This indicates the presence of residual inversion layers on the surface of the substrate, they can be eliminated by plasmachemical or chemical-dynamic methods.

The insulation resistance of samples with CV-characteristics of the Curve 4 type (Fig. 1) reached  $R_{con} \approx 200$ -600 k $\Omega$ , and  $J_{GR} \approx 50$ -100  $\mu$ A/cm<sup>2</sup>. From the above, it is possible to conclude that it is possible to estimate the conductivity of surface inversion channels based on the volt-farad characteristics.

The causes of ILs are known and studied [15]. The key factor in their formation is an increase in the resistivity of the substrate, since with an increase in  $\rho$  of the material, a smaller amount of impurities is needed to change the surface conductivity to the opposite [16]. In most cases, an inversion layer is already present on p-type silicon with  $\rho$ =1-10 Ohm·cm [17]. In the case of a thermal oxidation operation, the possible technological reasons for the appearance of inversion are improper chemical treatment of substrates, the presence of alkali metal impurities in deionized water, quartz vessels, or a quartz reactor, and carrier gases. However, the appearance of ILs during boron diffusion is caused by the redistribution of impurities in SiO<sub>2</sub> and their diffusion to the Si-SiO<sub>2</sub> interface [18]. These impurities were introduced into the oxide during previous thermal operations and diffused into the surface layer of silicon due to the high total duration of thermal treatments. Another factor that contributes to the formation of ILs with a high total duration of thermal operations is the diffusion of boron atoms from the near-surface layers of silicon into the oxide, since the segregation coefficient of boron is below unity [19].

The probability of the appearance of inversion layers can be minimized by careful control of carrier gases, deionized water for the presence of alkali metals, and periodic purging of quartz reactors with hydrochloric acid vapors. It is possible to increase the resistance of the insulation of REs and GR by forming regions of restriction of leakage channels in the gaps between active elements of the PD isotype with the substrate material [14]. It is possible to reduce the influence of the inversion layers of the periphery of photodiode crystals on the level of dark currents of the GR when the masking oxide is etched from the periphery and new film is formed in the dry oxygen atmosphere during the operation of drive-in of phosphorus [20].

### B) Reduction of the thickness of anti-reflective SiO<sub>2</sub> in the process of PDs manufacturing.

During the serial production of silicon *p-i-n* PDs, a decrease in the thickness of the ARC was noticed in the process of technological operations after its formation, this factor led to a decrease in responsivity, since the responsivity of the PD is directly proportional to the reflection coefficient of the anti-reflective film [21]:

$$S_{\lambda} = (1 - R)TQ\alpha_{p-n} \frac{\lambda}{1.24} \tag{2}$$

where R is the ARCs reflection coefficient; T is the transmission coefficient of the input window or optical filter; Q is the quantum output of the internal photoeffect;  $\alpha_{p-n}$  is the collection coefficient of minor charge carriers generated by radiation in the active region of the photodiode.

When studying what was described, it was seen that the reason for the decrease in  $d_{SiO2}$  is chemical treatment (CT). Accordingly, it was decided to study the influence of CT on the thickness of SiO<sub>2</sub>.

To clean the substrates, we used CT in boiling solutions of acids with the composition indicated in Table 1, the treatment duration was 10 minutes. To study the change in  $d_{SiO2}$  in the process of washing before and after operations, the thickness of this coating was measured.

**Table 1.** The composition of acid solutions for CT of silicon substrates and the change in  $d_{SiO2}$  during the operation

| Solution                                                                        | Composition | $\Delta d_{ m SiO2}$ , nm |

|---------------------------------------------------------------------------------|-------------|---------------------------|

| H <sub>2</sub> SO <sub>4</sub> :H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O | 4:1:1       | 6-7                       |

| HNO <sub>3</sub> :H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O               | 1:1:1       | 8-9                       |

| NH <sub>4</sub> OH:H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O              | 5:1:1       | 16-17                     |

Taking into account that after the formation of the anti-reflective oxide, according to the technological route, three more 3-stage washings are carried out, which will reduce  $d_{SiO2}$  by 90-100 nm, it is necessary to increase the duration of drive-in of phosphorus, and, accordingly, the thickness of ARC.

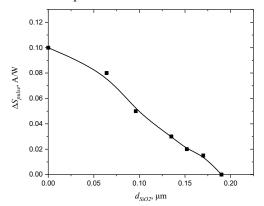

To be able to estimate the drop in responsivity ( $\Delta S_{pulse}$ ) of the PD as a result of  $d_{SiO2}$  reduction, a graph of the dependence of  $\Delta S_{pulse}$  on the ARC thickness was obtained (Fig. 2). The initial responsivity of the PD crystal was measured at  $d_{SiO2} \approx 0.18$  µm and the oxide was digested layer by layer in a slow etchant HF: H2O=1:10. After each etching process,  $S_{pulse}$  measurements were also performed.

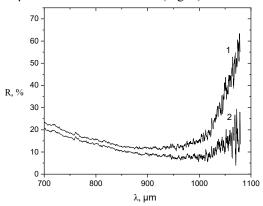

Reflectance spectra of PDs were obtained at  $d_{SiO2} \approx 0.170 - 0.175 \,\mu\text{m}$  and PDs without ARC (Fig. 3).

**Figure 2.** Experimental graph of the dependence of the drop in responsivity on the thickness of the anti-reflective coating

**Figure 3.** PDs reflection spectra: 1 - without ARC;  $2 - d_{SiO2} \approx 0.17 - 0.175 \ \mu m$

From Fig. 3, it can be seen that the reflection minimum of the investigated film is at  $\lambda \approx 1.01-1.02$  µm due to the deviation of the film thickness from the optimized for  $\lambda \approx 1.064$  µm. The reflection coefficient of PD without ARC is  $R \approx 45-50\%$  at the working wavelength, and with a thickness of anti-reflective silicon dioxide of 0.17-0.175 µm,  $R \approx 15-20\%$ . At  $d_{SiO2}=0.18-0.19$  µm at  $\lambda \approx 1.064$  µm, R=5-7%.

Changing the thickness of the masking and brightening coatings is also possible during photolithography, removal of phosphorosilicate (PSG) or borosilicate (BSG) glasses, and chemical dynamic polishing (CDP).

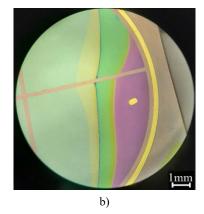

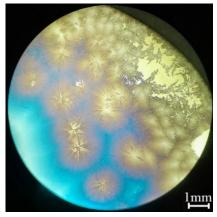

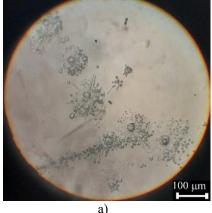

In particular, when etching the oxide during photolithography or when removing PSG/BSG in hydrofluoric acid, it is not permissible to remove the cassette with plates from the solution for a long time, as this leads to uneven etching of the surface (Fig. 4) due to the flow of the etchant on the surface of the substrate. Accordingly, non-uniformity of the film thickness can lead to scattered responsivity or uneven etching of the oxide during subsequent photolithography.

Figure 4. Image of uneven thickness of masking (a) and anti-reflective (b) SiO<sub>2</sub>

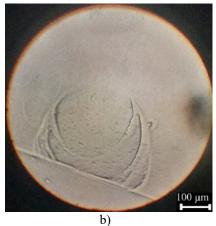

In order to carry out the CDP of the reverse side of the substrate, the front side is covered with a chemically resistant varnish [22]. If the thickness of the varnish is insufficient during drying, it is possible to form thinnings or punctures through which undesirable etching of the working surface of the crystal occurs. The consequence of thinning is spot etching of the oxide over the entire surface of the RE (Fig. 5 a), and in the case of punctures, the seepage of the etchant under the varnish and local etching of  $SiO_2$  (Fig. 5, b) or even silicon, which can lead to a breakdown of the p-n junction. To avoid the described situation, it is worth applying a double layer of varnish with intermediate drying.

Figure 5. Image of the dispersion of the thickness of the oxide film after CDP due to the thinning of the varnish (a) and punctures (b)

#### B) Defect formation during thermal oxidation

The most important condition for obtaining high-quality silicon oxide is the cleanliness of the plate before oxidation. The presence of impurities on the surface of silicon before oxidation or during the process of oxide growth negatively affects the uniformity of the film and the electrical properties of the interface.

On an uneven, contaminated surface, the grown or applied oxide contains inclusions of cristobalite (Fig. 6), which are undesirable in all classic cases of using oxide films of silicon technology. Cristobalite has a higher density than quartz glass, and the boundaries between amorphous regions and denser crystalline regions represent voids, which can be filled both with impurities from the surface and with a diffusant in the diffusion process [23]. A necessary condition for obtaining high-quality  $SiO_2$  is the polishing of the surface of the substrates followed by chemical treatment. Ultrasonic cleaning is also possible.

Packing defects are often formed during oxidation in silicon [24]. The formation of these defects on the surface of the plates occurs for several reasons. The first is mechanical damage to the surface of the substrate during cutting or grinding. If such damages, for example, scratches or cutting marks, are not removed by subsequent chemical polishing, then they can become local areas of nucleation of packaging defects (Fig. 7a).

**Figure 6.** Image of silicon oxide with cristobalite inclusions

**Figure 7.** Image of structural defects in the areas of mechanical disturbances (a) and swirl defects (b) on the surface of plates (plates after selective etching)

The second reason for the formation of packing defects (in the absence of mechanical damage on the surface) is related to the presence of growth and so-called swirl defects in the plates [25], since complexes of point defects with a swirl distribution are the seeds for packing defects during oxidation (Fig. 7b). Note that the defects formed during oxidation have an internodal nature and are associated with the accumulation and condensation of excess silicon atoms generated as a result of oxygen diffusion in silicon. It is the internodal silicon atoms that form point defect clusters in the areas of mechanical surface disturbances.

Another mechanism for the formation of structural defects during oxidation can be mechanical stresses introduced as a result of the difference in the thermal expansion coefficients of Si and SiO<sub>2</sub> [26]. But we did not observe the formation of defects by this mechanism.

It is worth noting that during the diffusion of phosphorus, clusters of packing defects are areas of dislocation generation. A high density of structural defects on the plate surface negatively affects the dark currents of photodiodes [27,28]. In order to avoid defect formation, it is worth using dislocation-free silicon, performing the CDP operation after mechanical processing of the wafers, and clearly controlling the substrates before thermal operations.

#### **CONCLUSIONS**

- 1. The problems of masking and anti-reflective SiO<sub>2</sub> in the technology of silicon *p-i-n* photodiodes were investigated.

- 2. The reason for the decrease in the insulation resistance of photosensitive elements in multi-element photodiodes is caused by the presence of surface inversion channels at the Si-SiO<sub>2</sub> interface. Inversion layers can be detected by measuring CV-characteristics.

- 3. Chemical treatment of oxidized substrates in boiling acid solutions helps to reduce the thickness of the oxide film.

- 4. When removing the cassette with oxidized plates from the solution during SiO<sub>2</sub>, BSG or PSG etching, uneven etching of the film is possible due to the flow of the etchant on the plate.

- 5. Oxidation of contaminated or uneven substrates can be accompanied by the formation of oxide with the inclusion of cristobalite.

- 6. Defect formation during thermal oxidation occurs in areas of mechanical disturbances or growth defects.

#### ORCID ID

**Mykola S. Kukurudziak,** https://orcid.org/0000-0002-0059-1387

#### REFERENCES

- [1] M. McClish, R. Farrell, R. Myers, F. Olschner, G. Entine, and K.S. Shah, Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, **567**(1), 36 (2006). https://doi.org/10.1016/j.nima.2006.05.055

- [2] A. Rahim, J. Goyvaerts, and B. Szelag, IEEE Journal of Selected Topics in Quantum Electronics, 25(5), 1 (2019). https://doi.org/10.1109/JSTQE.2019.2915949

- [3] S. Zhang, Y. Yao, and D. Hu, Energies, 12(6), 1168 (2019). https://doi.org/10.3390/en12061168

- [4] G. Gerlach, and K. Maser, Advances in condensed matter Physics, 2016, 7545632 (2016). https://doi.org/10.1155/2016/7545632

- [5] S.W. Glunz, F. Feldmann, Solar Energy Materials and Solar Cells, 185, 260 (2018). https://doi.org/10.1016/j.solmat.2018.04.029

- [6] A.A. Prishya, L. Chopra, Materials Today: Proceedings, 72, 1471 (2023). https://doi.org/10.1016/j.matpr.2022.09.348

- [7] O.V. Aleksandrov, and A.I. Dus, Physics and technology of semiconductors, 45(4), 474 (2011). (in Russian)

- [8] H. Mizobata, Y. Wada, M. Nozaki, Applied Physics Express, 13(8), 081001 (2020). https://doi.org/10.35848/1882-0786/aba320

- [9] J. Vanhellemont, and E. Simoen, Journal of the electrochemical society, 154(7), H572 (2007). https://doi.org/10.1149/1.2732221

- [10] M.S. Kukurudziak, Physics and Chemistry of Solid State, 23(4), 756 (2022). https://doi.org/10.15330/pcss.23.4.756-763

- [11] C.T. Sah, H. Sello, and D.A. Tremere, J. Phys. Chem. Solids, 11, 288 (1959). https://doi.org/10.1016/0022-3697(59)90229-X

- [12] S.B. Khan, S. Irfan, Z. Zhuanghao, and S.L. Lee, Materials, 12(9), 1483 (2019). https://doi.org/10.3390/ma12091483

- [13] F.A. Abdullin, V.E. Pautkin, E.A. Pecherskaya, A.V. Pecherskiy, D.V. Artamonov, and K.O. Nikolaev, in: 2019 International Seminar on Electron Devices Design and Production (SED), IEEE, (2019), pp. 1-4. https://doi.org/10.1109/SED.2019.8798467

- [14] M. Kukurudziak, Radioelectronic and Computer Systems, 105(1), 92 (2023). https://doi.org/10.32620/reks.2023.1.07

- [15] V.M. Lytvynenko, I.M. Vikulin, Bulletin of the Kherson National Technical University, (1), 46 (2018). (in Ukrainian)

- [16] Yu. O. Kruglyak, and M.V. Strikha, Sensor Electronics and Microsystem Technologies, 16(2), 5 (2019). https://doi.org/10.18524/1815-7459.2019.2.171224 (in Ukrainian)

- [17] M.M. Atalla, E. Tannenbaum, and E.J. Scheibner, Bell System Tech. J. 38, 749 (1959).

- [18] M.S. Kukurudziak, and E.V. Maistruk, in: 2022 IEEE 3rd KhPI Week on Advanced Technology (KhPIWeek) (IEEE, Kharkiv, 2022), pp. 1-6. https://doi.org/10.1109/KhPIWeek57572.2022.9916420

- [19] H. Chen, K. Morita, X. Ma, Z. Chen, and Y. Wang, Solar Energy Materials and Solar Cells, 203, 110169 (2019). https://doi.org/10.1016/j.solmat.2019.110169

- [20] M.S. Kukurudziak, Journal of nano- and electronic physics, 14(1), 01023 (2022). https://doi.org/10.21272/jnep.14(1).01023

- [21] A.V. Fedorenko, Technology and design in electronic equipment, 17(3-4), 17 (2020). https://doi.org/10.15222/ TKEA2020.3-4.17 (in Ukrainian)

- [22] M.S. Kukurudziak, Surface Chemistry, Physics and Technology, 14(1), 42 (2023). https://doi.org/10.15407/hftp14.01.042 (in Ukrainian)

- [23] K.L. Milton, T.R. Durrant, T. Cobos Freire, and A.L. Shluger, Materials, 16(4), 1382 (2023). https://doi.org/10.3390/ma16041382

- [24] F. Dai, and L. Zhang, Materials Science in Semiconductor Processing, 153, 107187 (2023). https://doi.org/10.1016/j.mssp.2022.107187

- [25] R. Tognato, Physica Status Solidi, 98(2), 681 (2022). https://doi.org/10.1515/9783112501825-048

- [26] T. Middelmann, A. Walkov, G. Bartl, and R. Schödel, Physical Review B, 92(17), 174113 (2015). https://doi.org/10.1103/PhysRevB.92.174113

- [27] B. Son, Y. Lin, K.H. Lee, Q. Chen, and C.S. Tan, Journal of Applied Physics, 127(20), 203105 (2020). https://doi.org/10.1063/5.0005112

- [28] M.S. Kukurudziak, Journal of nano- and electronic physics, 14(4), 04015 (2022). https://doi.org/10.21272/jnep.14(4).04015

# ПРОБЛЕМИ МАСКУЮЧОГО ТА ПРОСВІТЛЯЮЧОГО SiO $_2$ В КРЕМНІЄВІЙ ТЕХНОЛОГІЇ Микола С. Кукурудзяк $^{a,b}$

<sup>а</sup>АТ «Центральне конструкторське бюро Ритм», 58032, м. Чернівці, вул. Головна, 244, Україна  $^{b}$ Чернівецький національний університет імені Юрія Федьковича, 58002, м. Чернівці, вул. Коцюбинського, 2, Україна В статті досліджено проблематику термічного окиснення кремнію. Окиснення відіграє важливу роль в планарній технології, яка в свою чергу є основою технології кремнієвих інтегральних мікросхем, фотоприймачів та інших твердотільних засобів електроніки. При виготовленні нами кремнієвих *p-і-п* фотодіодів побачено ряд систематичних видів браку та погіршень параметрів виробів спричинених деградацією маскуючого чи просвітляючого покриттів в процесі виготовлення. Спостерігалось зниження опору ізоляції фоточутливих елементів в багатоелементних фотодіодах, що сприяло зростаню темнових струмів. Також виявлено зниження чутливості виробів внаслідок деградації товщини чи структури просвітляючого покриття під час технологічних операцій та ін. Встановлено, що причиною зниження опору ізоляції є утворення інверсійних шарів на межі розділу Si-SiO<sub>2</sub>, наявність яких можна виявити при вимірюванні CV-характеристик. Також встановлено, що хімічна обробка підкладок із SiO<sub>2</sub> в кип'ячих розчинах кислот сприяє зменшенню товщини оксиду. Для уникнення відхилення товщини плівки від умови мінімуму відбивання варто вирощувати товстішший шар просвітляючого покриття. Зауважено, що при травленні оксиду під час фотолітографії чи при зніманні ФСС/БСС в плавиковій кислоті не припустимо виймати касету з пластинами із розчину на тривалий час, оскільки це призводить до нерівномірного травлення плівки внаслідок стікання травника по поверхні підкладки. Наведено причини дефектоутворення в Si та SiO2 під час окиснення. Так, при неналежній механічній та хімічній обробці пластин можливе утворення включень кристобалітів в плівку під час окиснення. Кристобаліт володіє вищою густиною ніж кварцове скло, а межі між аморфними областями і більш щільними кристалічними областями представляють порожнечі, які можуть бути заповнені як забрудненнями з поверхні так і дифузантом в процесі дифузії. Також під час окиснення в кремнію часто утворюються дефекти упаковки. Центрами зародження дефектів можуть бути механічні пошкодження поверхні пластини чи ростові дефекти.

Ключові слова: кремній; фотодіод; окиснення; оксид кремнію; вольт-фарадна характеристика; просвітляюча плівка